- 您现在的位置:买卖IC网 > Sheet目录369 > W972GG6JB-3I (Winbond Electronics)IC DDR2 SDRAM 2GBITS 84WBGA

�� �

�

�

�W972GG6JB�

�7.3�

�7.3.1�

�Command� Function�

�Bank� Activate� Command�

�(� CS� ="L",� RAS� ="L",� CAS� ="H",� WE� ="H",� BA0,� BA1,� BA2=Bank,� A0� to� A13� be� row� address)�

�The� Bank� Activate� command� must� be� applied� before� any� Read� or� Write� operation� can� be� executed.�

�Immediately� after� the� bank� active� command,� the� DDR2� SDRAM� can� accept� a� read� or� write� command�

�on� the� following� clock� cycle.� If� a� Read/Write� command� is� issued� to� a� bank� that� has� not� satisfied� the�

�t� RCDmin� specification,� then� additive� latency� must� be� programmed� into� the� device� to� delay� when� the�

�Read/Write� command� is� internally� issued� to� the� device.� The� additive� latency� value� must� be� chosen� to�

�assure� t� RCDmin� is� satisfied.� Additive� latencies� of� 0,� 1,� 2,� 3,� 4,� 5� and� 6� are� supported.� Once� a� bank� has�

�been� activated� it� must� be� precharged� before� another� Bank� Activate� command� can� be� applied� to� the�

�same� bank.� The� bank� active� and� precharge� times� are� defined� as� t� RAS� and� t� RP� ,� respectively.� The�

�minimum� time� interval� between� successive� Bank� Activate� commands� to� the� same� bank� is� determined�

�by� the� RAS� cycle� time� of� the� device� (t� RC� ).� The� minimum� time� interval� between� Bank� Activate�

�commands� is� t� RRD� .�

�In� order� to� ensure� that� components� with� 8� internal� memory� banks� do� not� exceed� the� instantaneous�

�current� supplying� capability,� certain� restrictions� on� operation� of� the� 8� banks� must� be� observed.� There�

�are� two� rules.� One� for� restricting� the� number� of� sequential� ACT� commands� that� can� be� issued� and�

�another� for� allowing� more� time� for� RAS� precharge� for� a� Precharge� All� command.� The� rules� are� as�

�follows:�

�?�

�?�

�Sequential� Bank� Activation� Restriction:� No� more� than� 4� banks� may� be� activated� in� a� rolling� t� FAW�

�window.� Converting� to� clocks� is� done� by� dividing� t� FAW� [nS]� by� t� CK� (avg)[ns],� and� rounding� up� to�

�next� integer� value.� As� an� example� of� the� rolling� window,� if� RU{� (t� FAW� /� t� CK� (avg)� }� is� 10� clocks,�

�and� an� activate� command� is� issued� in� clock� N,� no� more� than� three� further� activate� commands�

�may� be� issued� at� or� between� clock� N+1� and� N+9.�

�Precharge� All� Allowance:� t� RP� for� a� Precharge� All� command� is� equal� to� tn� RP� +� 1� x� n� CK� ,� where�

�tn� RP� =� RU{� t� RP� /� t� CK� (avg)� }� and� t� RP� is� the� value� for� a� single� bank� precharge.�

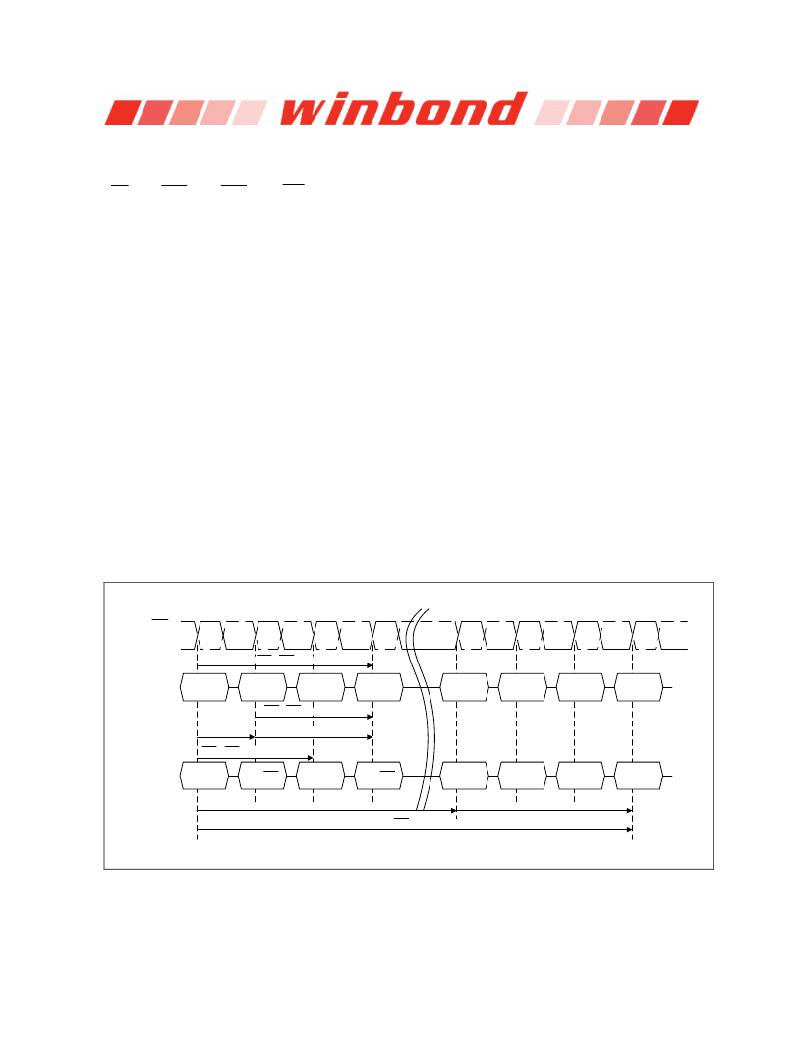

�T0�

�T1�

�T2�

�T3�

�Tn�

�Tn+1�

�Tn+2�

�Tn+3�

�CLK�

�CLK�

�Internal� RAS� -� RAS� delay� (� ≥� t� RCD� min)�

�Address�

�Bank� A�

�Row� Addr.�

�Bank� A�

�Col.� Addr.�

�Bank� B�

�Row� Addr.�

�Bank� B�

�Col.� Addr.�

�Bank� A�

�Addr.�

�Bank� B�

�Addr.�

�Bank� A�

�Row� Addr.�

�CAS - CAS delay time(t� CCD� )�

�t� RCD� =� 1�

�Additive Latency delay(AL)�

�Read� Begins�

�RAS - RAS delay time(≥ t� RRD� )�

�Command�

�Bank� A�

�Activate�

�Bank� A�

�Post� CAS�

�Read�

�Bank� B�

�Activate�

�Bank� B�

�Post� CAS�

�Read�

�Bank� A�

�Precharge�

�Bank� B�

�Precharge�

�Bank� A�

�Activate�

�Bank� Active� (� ≥� t� RAS� )�

�Bank� Precharge� time� (� ≥� t� RP� )�

�RAS Cycle time (≥ t� RC� )�

�Figure� 12� –� Bank� activate� command� cycle:� t� RCD� =� 3,� AL� =� 2,� t� RP� =� 3,� t� RRD� =� 2,� t� CCD� =� 2�

�Publication� Release� Date:� Nov.� 29,� 2011�

�-� 20� -�

�Revision� A02�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9751G6IB-25

IC DDR2-800 SDRAM 512MB 84-WBGA

W9751G6KB-25

IC DDR2 SDRAM 512MBIT 84WBGA

W9812G6JH-6I

IC SDRAM 128MBIT 54TSOPII

W9816G6IH-6I

IC SDRAM 16MBIT 50TSOPII

W9825G6JH-6I

IC SDRAM 256MBIT 54TSOPII

W9864G6JH-6I

IC SDRAM 64MBIT 54TSOPII

WM-5614

CABINET WALL MOUNT 37.25X17.9"

WRR-2244

RACK WALL MOUNT RELAY 42" X 19"

相关代理商/技术参数

W972GG8JB

制造商:WINBOND 制造商全称:Winbond 功能描述:32M ??′ 8 BANKS ??′ 8 BIT DDR2 SDRAM

W972GG8JB-18

制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 1.875NS BGA

W972GG8JB-25

制造商:Winbond Electronics Corp 功能描述:2GMB DDRII 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 60WBGA

W972GG8JB-25I

制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 80WBGA

W972GG8JB-3

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 2G-Bit 256Mx8 1.8V 60-Pin WBGA 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 3NS

W9751G6IB-25

功能描述:IC DDR2-800 SDRAM 512MB 84-WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.173",4.40mm 宽) 供应商设备封装:8-MFP 包装:带卷 (TR)

W9751G6JB

制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM

W9751G6JB-25

制造商:Winbond Electronics Corp 功能描述:512GB DDRII